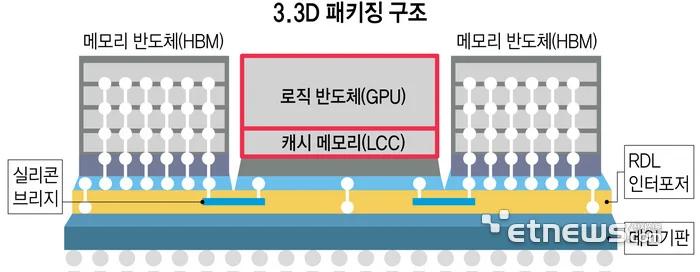

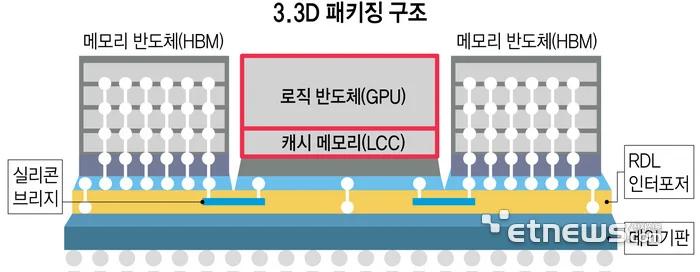

三星电子先进封装部门正主导开发“半导体3.3D先进封装技术”,预计2026年第二季度量产,该技术将逻辑芯片与HBM连接,并通过3D堆叠技术提升AI半导体芯片性能。

🌟 三星电子的3.3D封装技术,通过安装RDL中介层替代传统的硅中介层,实现逻辑芯片与高带宽存储器(HBM)的高效连接,提升数据传输速度和稳定性。

🔧 该技术采用3D堆叠方法,将GPU(AI计算芯片)垂直堆叠在LCC(SRAM缓存)之上,实现更紧凑的芯片结构和更高的集成度。

🎯 目标是将逻辑芯片和缓存部分键合为一体,类似于三星电子现有的X-Cube技术,但进一步优化,以适应AI芯片的高性能需求。

📉 通过这种先进封装技术,三星旨在降低芯片体积,提高能效比,为AI半导体市场提供更具竞争力的解决方案。

🚀 该技术的量产预计在2026年第二季度开始,届时将有望推动AI芯片的进一步发展和应用。

据报道,三星电子先进封装(AVP)部门正在主导开发“半导体3.3D先进封装技术”,目标应用于AI半导体芯片,2026年第二季度量产。该技术通过安装RDL中介层替代硅中介层来连接逻辑芯片和HBM;并通过3D堆叠技术将逻辑芯片堆叠在LLC上。 韩媒给出的封装概念图显示,这一 3.3D 封装技术整合了三星电子多项先进异构集成技术。▲ 图源 ETNews 技术概念图中 GPU(AI 计算芯片)垂直堆叠在 LCC(即 SRAM 缓存)之上,目标两部分键合为一体,年季这点类似于三星电子现有 X-Cube 3