文 | 半导体产业纵横,作者 | 方圆

随着AI 技术尤其是大语言模型的快速发展,AI 算力需求呈爆发式增长。OpenAI 测算显示,全球 AI 训练算力需求每 3.4 个月翻一番,2012 年以来已增长超 500,000 倍。这种迅猛的增长态势对数据中心的算力和数据传输能力带来了前所未有的挑战。数据中心作为 AI 算力的承载核心,需要处理海量的数据,这使得其内部的数据流量呈指数级增长。例如,大规模的 AI 训练集群中,服务器之间需要频繁地交换大量的数据,以支持模型的训练和优化。传统的数据传输方式在面对如此巨大的数据流量时,逐渐显露出其局限性。

光模块作为数据中心中实现光电信号转换的关键组件,其性能直接影响着数据传输的速率、容量和效率。在高算力需求的背景下,传统光模块面临着诸多挑战。

随着数据量的不断增加,对光模块的传输速率要求越来越高。从早期的10G、25G,到如今的 100G、400G,甚至向 1.6T 及更高速率迈进,传统光模块在提升速率方面遇到了技术瓶颈。其次,高速率传输带来的高功耗问题也日益突出。高功耗不仅增加了数据中心的运营成本,还对散热系统提出了更高的要求,增加了数据中心的建设和维护难度。此外,传统光模块在尺寸和集成度方面也难以满足数据中心日益紧凑的布局需求。为了应对这些挑战,共封装光学(CPO)技术应运而生。

优势亮眼,短板也明显

CPO其核心在于将光引擎与交换芯片通过先进的封装技术集成在同一基板上。在传统的可插拔光模块方案中,光模块通过可插拔接口与交换机的印刷电路板(PCB)相连,电信号需要经过数厘米长的 PCB 走线才能到达光模块进行光电转换。这一过程中,电信号会受到 PCB 走线的电阻、电容和电感等因素的影响,导致信号衰减、失真和延迟增加。而 CPO 技术通过将光引擎与交换芯片紧密集成,极大地缩短了电信号在芯片和光引擎之间的传输距离,通常可将传输距离缩短至毫米级。这种短距离的传输方式能够有效减少信号在传输过程中的损耗和干扰,提高信号的完整性和传输质量。

但其目前也存在着一些短板。

技术上还不够成熟,导致成本一直下不来,这是个大问题。现在产业链还有不少难关要过:台积电的硅光晶圆良率才 65%,光迅科技测试发现,CPO 模块端到端的耦合损耗波动有 ±2dB,比可插拔模块的 ±0.5dB 差远了。这些技术问题直接让单个模块的生产成本比老方案高 3-5 倍,1.6T 端口的 CPO 方案总成本要 2800 美元一个端口,是可插拔模块的 2.3 倍。就算以后量产规模上去了,想把成本差距缩小,估计也得 3-5 年。

运维方面的变化也是个麻烦事。因为不能像传统光模块那样随便插拔,CPO 模块少了即插即用的方便。Facebook 模拟测试过,用 CPO 架构的话,得多配 30% 的冗余交换芯片来应对故障,这样一来,总体成本就得多花 18%。思科也研究过,CPO 模块坏了,平均要 72 小时才能修好,是可插拔模块的 6 倍。对于那些要求 99.999% 可用性的金融数据中心来说,这是致命的问题,搞不好一小时就得损失几十万美元。

还有就是行业标准太乱,也拖慢了 CPO 产业化的脚步。现在 CPO 领域有 COBO、OIF、OpenEye 等好几个标准阵营,封装尺寸从 35mm×35mm 到 58mm×58mm 不等,供电规范从 3.3V 到 12V 都有,热管理方案里液冷占比也从 30% 到 100% 不一样。这种混乱让设备商十分头疼,得为不同方案开发适配接口,研发成本平白多了 40% 以上。比如有头部交换机厂商,为了兼容三种主流标准,光测试环节就多花了 2000 万美元,这显然会拖慢技术落地的速度。

谁在主导CPO?

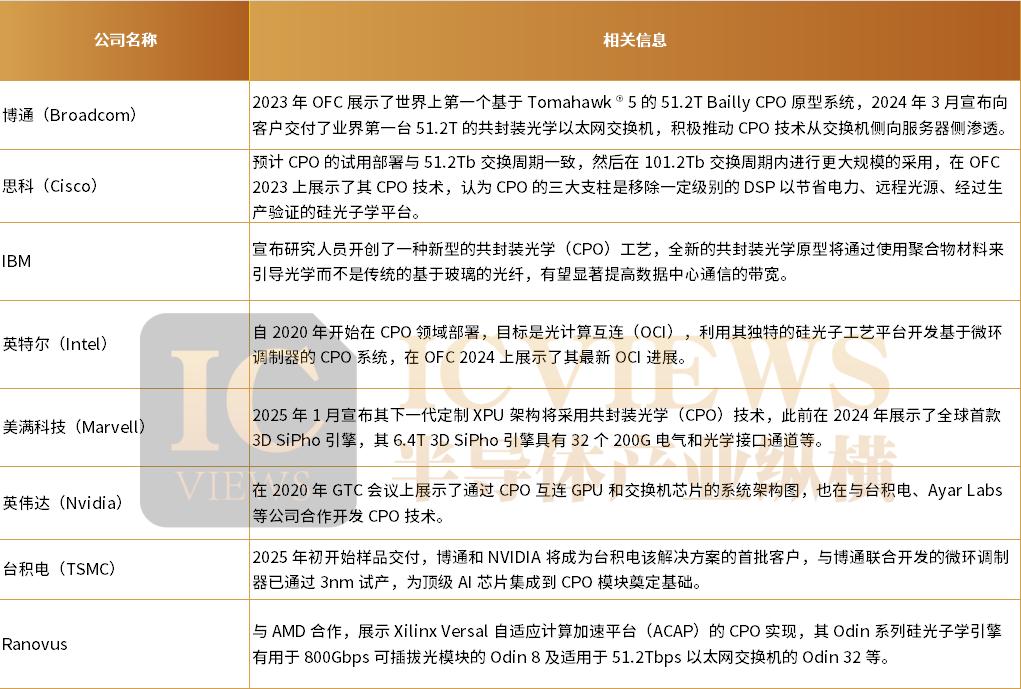

在 CPO 技术的研发和应用方面,众多行业巨头积极布局,发挥着引领作用。

AMD 与 Ranovus 的合作始于 CPO 技术的早期探索。2020 年 OFC 上,Ranovus 首次展示了基于多波长量子点激光器(QDL)和磁共振器技术的 Odin 系列硅光子学引擎,其功耗和成本较当时的替代方案显著降低。2021 年,Ranovus 推出第二代 CPO 光学引擎,采用模拟驱动方法消除重定时器需求,进一步优化成本与功耗,并将相关元件集成到单个电子光子 IC 中。2022 年,双方合作展示了 Xilinx Versal 自适应计算加速平台的 CPO 实现,利用 Odin 800-Gbps CPO 2.0 技术,简化电路板布线并降低功耗。到 2023 年 OFC,两家公司又演示了 Versal 自适应 SoC 与 Odin 800G 直接驱动光学引擎及第三方模块的互操作性,其光学引擎基于 GlobalFoundries 的硅光子平台构建,为超大规模数据中心的 AI/ML 工作负载提供了灵活且低功耗的解决方案。

博通则积极推动 CPO 技术从交换机侧向服务器侧渗透。2021 年,博通提前宣布了配备 CPO 光学器件的下一代交换芯片系列,包括计划于 2022 年底上市的 25.6Tb Humboldt 和后续的 51.2T Bailly,并提及与 CPU、GPU 共同封装的未来规划。2023 年 OFC 上,博通展示了基于 Tomahawk5 的 51.2T Bailly CPO 原型系统和基于 Tomahawk4 的 25.6T Humboldt CPO 系统,其全 CMOS EIC 集成了低功耗 TIA 和光学 MUX/DEMUX,将光引擎带宽提升至 6.4T,显著降低光互连功率。2024 年 3 月,博通向客户交付了业界首台 51.2T CPO 以太网交换机,集成 8 个 6.4Tbps 硅光子学光学引擎与 Tomahawk 5 交换芯片,功耗较可插拔光模块解决方案大幅降低,未来还计划将 CPO 技术拓展至算力芯片,追求更高带宽。

思科对 CPO 技术的落地节奏有着明确判断,认为其三大支柱在于移除部分 DSP 以节省电力、采用远程光源和依托生产验证的硅光子学平台,这些创新可将连接所需功率降低最多 50%,使固定系统总功率降低 25-30%。2023 年 OFC 上,思科的 CPO 演示展现了关键技术优势,其在硅光子学 IC 上实现了 400G FR4 所需的多路复用 / 解复用器,解决了光学元件小型化难题,能支持多种数据中心光学器件类型。思科预计,CPO 的试用部署将与 51.2Tb 交换周期同步,在 101.2Tb 交换周期实现更大规模应用。

IBM 与 Finisar 合作开发的 MOTION 项目,以独特的激光光源 2:1 冗余备份设计为亮点,适用于 LGA 及焊接式组装,旨在提升系统整体可靠性,与博通采用的外置可插拔光源方案形成差异。

英特尔自 2020 年起布局 CPO,以光计算互连(OCI)为最终目标。凭借在硅光子学领域的深厚积累,英特尔专注于可插拔光收发器和微环调制器技术研发,并利用自身独特的硅光子学工艺平台开发基于微环调制器的 CPO 系统。

Marvell 的 CPO 技术平台兼顾可插拔与共封装需求。2022 年 OFC 上,其第一代云优化 CPO 平台亮相,整合 2.5D/3D 高度集成硅光子学元件,包括激光器、TIA、驱动器及 PAM4 DSP,为 51.2T 交换机的 3.2T CPO 平台奠定基础。2023 年,Marvell 展示的新型每通道 200G 硅光子学光引擎,集成数百个组件,可灵活作为可插拔光学模块或 CPO 光学解决方案。

英伟达作为 GPU 领域领导者,同时布局交换机侧及 GPU 侧 CPO。其首席科学家 Bill Dally 在 2022 年 OFC 演讲中,详细阐述了采用密集波分复用(DWDM)的共封装光学器件目标,以及利用硅光子学交叉连接不同机架 GPU 计算引擎的构想。英伟达与 AyarLabs 合作,致力于开发高带宽、低延迟、超低功耗的光互连技术,以支持 AI/ML 架构的横向扩展,应对数据量快速增长的需求。

台积电则通过推出 COUPE 光学平台布局 CPO 领域。在 2024 年北美技术研讨会上,台积电介绍了基于硅光子的解决方案,目标是实现高达 12.8 Tbps 的带宽。其 COUPE 引擎采用 SoIC-X 封装技术,将 65nm 电子集成电路(EIC)与光子集成电路(PIC)结合,凭借低阻抗的 SoIC-X 互连实现高效用电,为数据中心未来的高带宽需求提供关键技术支撑。

棋逢对手

面对 CPO 技术的竞争,传统可插拔模块也在不断创新,以提升自身性能。

在速率突破层面,可插拔模块通过高阶调制与集成技术的协同,稳步向 1.6T 及以上速率演进。16QAM 等调制方式提升单波长数据密度,硅光子集成技术将光引擎尺寸压缩至标准封装范围内,使模块在保持 2km 级跨机架传输能力的同时,无需对现有数据中心的物理布线架构进行改造。这种技术路径的核心在于,在不打破成熟封装标准的前提下实现速率跃迁,其背后是对存量数据中心升级成本的精准控制 —— 避免因架构重构导致的额外投入,这对于中大型数据中心的平滑过渡具有不可替代的价值。

功耗优化的逻辑则体现了技术选择的务实性。不同于 CPO 通过缩短电信号路径实现的极致降耗,可插拔模块聚焦于现有架构下的能效提升:通过动态功率管理算法匹配数据流量波动,新型低热阻封装材料降低热耗散损耗,配合低功耗激光器驱动电路设计,在中短距离传输场景中实现单位带宽功耗的阶梯式下降。这种优化虽未触及传输距离的物理限制,却在技术成熟度与能效比之间找到了平衡,尤其适合对改造成本敏感的规模化部署场景。

未来,这两种技术并非“非此即彼” 的替代关系,而是将在数据中心的 “层级化网络” 中各司其职:CPO 凭借低延迟、高集成优势,主导机架内部的高密度互联;可插拔模块则依托灵活性与兼容性,覆盖跨机架、跨机房的中远距离传输。这种 “分层共存” 的格局,将推动光互连技术向更细分、更高效的方向演进。

同时,为了兼顾可维护性和能效提升,一些混合架构方案开始兴起。英伟达在Grace Hopper 超算中采用的 “可插拔 CPO” 架构颇具启示,通过标准化光电接口,实现光引擎与交换芯片的物理分离但电气直连。这种设计在保持可维护性的同时,将能效提升至 2.1pJ/bit,为技术过渡提供了新思路。这种混合架构方案在一定程度上融合了可插拔模块和 CPO 的优势,可能会在未来的市场中占据一席之地。

结语

在这场“量变”引发“质变”的技术革命中,共封装光学(CPO)技术凭借其在传输速率、功耗及集成度方面的巨大潜力,无疑成为了万众瞩目的焦点。

然而,正如本文所阐述的,CPO技术的产业化之路并非一片坦途,其在技术成熟度、成本控制、运维模式以及行业标准统一等方面仍面临严峻挑战。硅光晶圆良率、耦合损耗控制、高昂的初期投入、复杂的故障维护以及标准的混乱,都是横亘在CPO大规模商用化面前的“拦路虎”。这些挑战意味着CPO的全面普及可能还需要3-5年甚至更长时间的技术攻坚与产业链协同。

更多精彩内容,关注钛媒体微信号(ID:taimeiti),或者下载钛媒体App