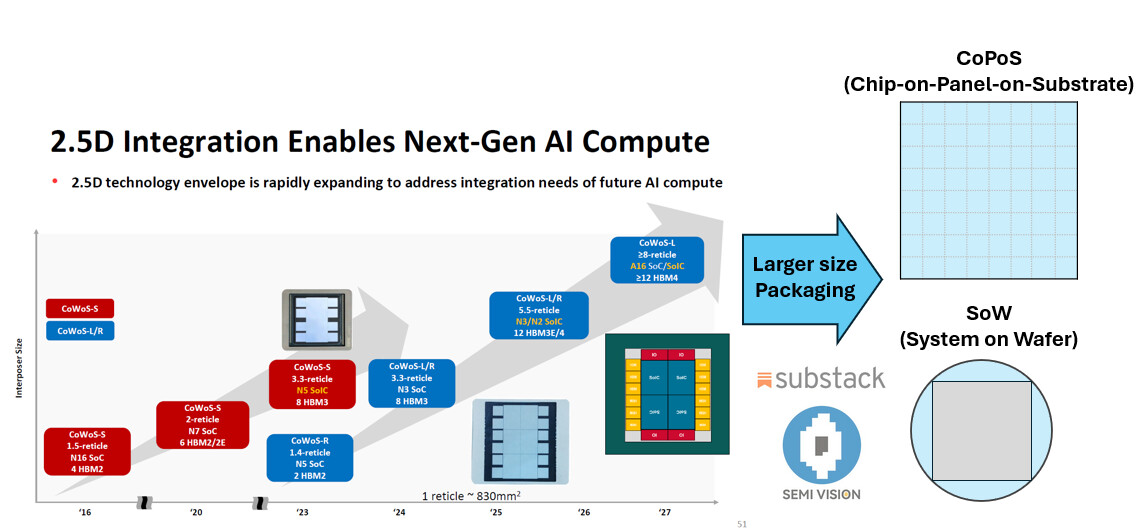

随着对日益增长的人工智能计算能力的需求不断增长,以及制造先进节点的难度加大,封装技术正迎来发展的黄金时代。如今,先进的加速器通常依赖于台积电的CoWoS模块,这些模块基于尺寸不超过120×150毫米的晶圆切割而成。

为了满足更多空间的需求,台积电公布了CoPoS(即“基板上面板上的芯片”)计划,该计划可以将基板尺寸扩展到310×310毫米甚至更大。通过从圆形晶圆转换为矩形面板,CoPoS可提供五倍以上的可用面积。

额外的表面使得在单个封装中集成额外的高带宽内存堆栈、多个I/O芯片和计算芯片成为可能。这也使面板级封装(PLP)脱颖而出。

与晶圆级封装(WLP)不同,PLP将组件组装在大型矩形面板上,从而提供更高的吞吐量和更低的单位成本。采用 PLP 的系统实际上将适用于量产,并且比 WLP 更快地实现迭代。

台积电将于 2026 年在其子公司 Visionchip 建立一条 CoPoS 试验线。2027 年,该试验工厂将专注于改进工艺,以在年底前满足合作伙伴的要求。量产预计将于 2028 年底至 2029 年初在台积电嘉义 AP7 园区开始。该园区因其现代化的基础设施和充足的空间而被选中,还将用于生产多芯片模块和晶圆系统技术。

NVIDIA 预计将成为 CoPoS 的首发合作伙伴。该公司计划利用更大的面板面积容纳多达 12 个 HBM4 芯片以及多个 GPU 芯片,从而显著提升 AI 工作负载的性能。同时,AMD 和博通将继续在其高端产品中使用台积电的 CoWoS-L 和 CoWoS-R 版本。

除了简单地增加尺寸之外,CoPoS 和 PLP 还可以与其他新兴技术(例如玻璃基板和硅光子学)协同工作。如果开发按计划进行,首批支持 CoPoS 的设备有望在 2029 年底上市。